# THE MODEL 1410 IS NOT RECOMMENDED FOR NEW PROJECTS

| Digital Pulse Density Output to Measure Acceleration                                                  | AVAILABLE G-RANGES |           |           |  |

|-------------------------------------------------------------------------------------------------------|--------------------|-----------|-----------|--|

| Drop-In Replacement for Model 1010                                                                    | FULL SCALE         | 20 PIN    | 20 PIN    |  |

| Integrated Sensor & Amplifier                                                                         | ACCELERATION       | JLCC      | LCC       |  |

| • -55 to +125 °C Operation                                                                            | ± 2 g              | 1410J-002 | 1410L-002 |  |

| • +5 VDC, 2 mA Power (typical)                                                                        | ± 5 g              | 1410J-005 | 1410L-005 |  |

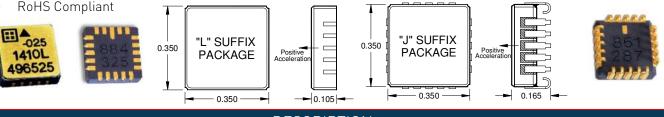

| <ul> <li>LCC or J-Lead Surface Mount Package</li> <li>Responds to DC &amp; AC Acceleration</li> </ul> | ± 10 g             | 1410J-010 | 1410L-010 |  |

| No External Reference Voltage                                                                         | ± 25 g             | 1410J-025 | 1410L-025 |  |

| <ul> <li>Easy Interface to Microprocessors, TTL/CMOS Compatible</li> </ul>                            | ± 50 g             | 1410J-050 | 1410L-050 |  |

| Nitrogen Damped & Hermetically Sealed                                                                 | ± 100 g            | 1410J-100 | 1410L-100 |  |

- Capacitive Micromachined & Serialized for Traceability •

- Good EMI Resistance

- **RoHS** Compliant

± 200 g

#### DESCRIPTION

The Model 1410 is an integrated accelerometer for use in zero to medium frequency instrumentation applications measuring Each miniature, hermetically sealed package acceleration. combines a micro-machined capacitive sense element and a custom integrated circuit that includes a sense amplifier and sigmadelta A/D converter. It is relatively insensitive to temperature changes and gradients. Each device is marked with a serial number on its top and bottom surfaces for traceability. An optional calibration test sheet (1410-TST) is also available which lists the measured bias, scale factor, linearity, operating current and frequency response.

1410J-200

1410L-200

| ZERO (DC) TO MEDIUM FREQUENCY APPLICATIONS |             |                            |                |               |                        |              |                        |       |

|--------------------------------------------|-------------|----------------------------|----------------|---------------|------------------------|--------------|------------------------|-------|

| ROBOTICS                                   | TILT        | VIBRATION                  | AUTOMOTIVE     | ІМРАСТ        | INSTRUMEN              |              | MONITOR                | OEM   |

|                                            |             |                            | PERFO          | RMANCE        |                        |              |                        |       |

| INPUT<br>RANGE                             | FI          | REQUENCY RES<br>(MIN, 3 DE |                |               | GITIVITY,<br>RENTIAL   | MAX.         | MECHANICAL<br>(0.1 MS) | SHOCK |

| a                                          |             | Hz                         |                | kHz/q         |                        |              | q (peak)               |       |

| ±2                                         | 0 - 400     |                            | 62.5           |               |                        | <u> </u>     |                        |       |

| ±5                                         |             | 0 – 500                    |                | 25            |                        | - 2000       |                        |       |

| ±10                                        |             | 0 – 700                    |                | 1             | 2.5                    |              |                        |       |

| ±25                                        |             | 0 - 1000                   |                | 5             |                        |              |                        |       |

| ±50                                        |             | 0 - 1300                   |                | 2.5           |                        | 5000         |                        |       |

| ±100                                       |             | 0 - 1600                   |                | 1.25<br>0.625 |                        |              |                        |       |

| ±200                                       |             | 0 - 1900                   |                |               |                        |              |                        |       |

| By Model: VDD=VR=5                         | 5.0 VDC, Fo | LK=250kHz, Tc=25°C         |                | Note 1: Sens  | sitivity typical at cl | ock frequer. | ncy 250kHz             |       |

|                                            |             | SPECIEIC                   | ATIONS SUBJECT | TO CHANGE     |                        | CF           |                        |       |

Silicon Designs, Inc. • 13905 NE 128th Street, Kirkland WA 98034 • Phone: 425-391-8329 • Fax: 425-391-0446 www.silicondesigns.com [page 1] 15-July-2020

| PERFORMANCE                                                          | E - ALL VERSI | DNS  |         |                    |

|----------------------------------------------------------------------|---------------|------|---------|--------------------|

| All Models: Unless otherwise specified VdD=VR=5.0 VDC, FcLK=250 kHz, |               |      |         |                    |

| PARAMETER                                                            | MIN           | TYP  | MAX     | UNITS              |

| Cross Axis Sensitivity                                               |               | 2    | 3       | ± %                |

| Bias Calibration Error <sup>1</sup>                                  |               | 0.2  | 0.5     | ± % of Fclк (span) |

| Bias Temperature Shift (Tc= -55 to +125°C) <sup>1</sup>              | -200          | 0    | +200    | (PPM of Fclk)/°C   |

| Scale Factor Calibration Error <sup>1,2</sup>                        |               | 0.75 | 2       | ± %                |

| Scale Factor Temperature Shift (Tc= -55 to +125°C) <sup>1</sup>      | 0             |      | +200    | PPM/°C             |

| Non-Linearity (-90 to +90% of Full Scale) <sup>1,2</sup>             |               | 0.5  | 1.0     | ± % of span        |

| Long Term Bias Stability                                             |               | 1000 | 2000    | ± PPM of span      |

| In Run Bias Stability                                                |               | 18   | 30      | ± PPM of span      |

| Long Term Scale Factor Stability                                     |               | 500  | 1000    | ± PPM              |

| Turn-On Transient (in less than 0.5ms)                               |               | 38   |         | ± PPM of span      |

| Operating Voltage (VDD vs. GND)                                      | 4.5           | 5.0  | 5.5     | Volts              |

| Operating Current (IDD + IvR) <sup>1</sup>                           |               | 2    | 3       | mA                 |

| Clock Input Voltage Range (with respect to GND)                      | -0.5          |      | Vdd+0.5 | Volts              |

| Mass 'L' Package (add 0.06 grams for 'J' package)                    |               | 0.62 |         | Grams              |

|                                                                      |               |      |         |                    |

Note 1: Tighter tolerances may be available on special order.

Note 2: 100g and greater versions are tested and specified from -65 to +65g

#### DC CHARACTERISTICS

| V <sub>DD</sub> =V <sub>R</sub> =5.0 VDC, T <sub>C</sub> = 55 to +125°C |                                        |           |     |     |       |                       |  |

|-------------------------------------------------------------------------|----------------------------------------|-----------|-----|-----|-------|-----------------------|--|

| PARAM                                                                   | IETER                                  | MIN       | TYP | MAX | UNITS | TEST CONDITIONS       |  |

| VT-                                                                     | Negative Going Threshold Voltage (CLK) | 0.9       | 1.7 |     | V     |                       |  |

| $V_{T+}$                                                                | Positive Going Threshold Voltage (CLK) |           | 3.0 | 3.7 | V     |                       |  |

| VH                                                                      | Hysteresis Voltage (CLK)               | 0.5       | 1.3 |     | V     |                       |  |

| Vol                                                                     | Output Low Voltage(CNT, DIR, CLK/2)    |           |     | 0.4 | V     | lo∟ = 2.0 mA          |  |

| Vон                                                                     | Output High Voltage(CNT, DIR, CLK/2)   | Vdd - 0.4 |     |     | V     | Iон = 2.0 mA          |  |

| lı                                                                      | Input Leakage Current (CLK)            |           |     | 10  | μΑ    | $V_1 = 0$ to $V_{DD}$ |  |

| Сю                                                                      | Pin Capacitance                        |           |     | 10  | рF    | 1 MHz, TA = 25°C      |  |

| ldd+lvr                                                                 | Operating Current                      |           | 2   | 3   | mA    | Fclk = 250kHz         |  |

# DC CHARACTERISTICS

| VDD=VR=5.0 VDC, Tc= -55 to +125°C, Load Capacitance=50pF. |     |     |      |       |  |  |

|-----------------------------------------------------------|-----|-----|------|-------|--|--|

| PARAMETER                                                 | MIN | TYP | MAX  | UNITS |  |  |

| CLK input frequency                                       | 100 | 250 | 1000 | kHz   |  |  |

| CLK input rise/fall time                                  |     |     | 50   | ns    |  |  |

| CLK duty cycle                                            | 45  | 50  | 55   | %     |  |  |

| CLK fall to DIR fall                                      | 40  | 85  | 195  | ns    |  |  |

| CLK fall to DIR rise                                      | 40  | 90  | 205  | ns    |  |  |

| CLK rise to valid CNT out                                 | 40  | 90  | 230  | ns    |  |  |

| CLK fall to CNT fall                                      | 40  | 85  | 205  | ns    |  |  |

| CLK fall to CLK/2 rise/fall                               | 40  | 90  | 210  | ns    |  |  |

## MAXIMUM RATINGS\*

| Case Operating Temperature <sup>4</sup>    | -55 to +125°C     | * NOTICE: Stresses greater than those listed above                                                        |

|--------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|

| Storage Temperature <sup>4</sup>           | -55 to +125°C     | may cause permanent damage to the device. These                                                           |

| Voltage on VDD to GND                      | -0.5V to 6.5V     | are stress ratings only. Functional operation of the                                                      |

| Voltage on Any Pin (except DV) to GND $^3$ | -0.5V to VDD+0.5V | device at or above these conditions is not implied.<br>Exposure to absolute maximum rating conditions for |

| Voltage on DV to GND <sup>5</sup>          | ±15V              | - extended periods may affect device reliability and                                                      |

| Power Dissipation                          | 20 mW             | lifespan.                                                                                                 |

Note 3: Voltages on pins other than DV, GND or Vod may exceed 0.5 volt above or below the supply voltages if current is limited to 1 mA. Note 4: Operation may continue with limited exposure up to 175°C. Minimal exposure over 125°C recommended for maximum lifespan. Note 5: The application of DV voltages higher than required to bring the output to positive full scale may cause device damage.

#### SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

Silicon Designs, Inc. • 13905 NE 128<sup>th</sup> Street, Kirkland WA 98034 • Phone: 425-391-8329 • Fax: 425-391-0446 <u>www.silicondesigns.com</u> [page 2] 15-July-2020

CLK

CNT

DIR

DIR

#### OPERATION

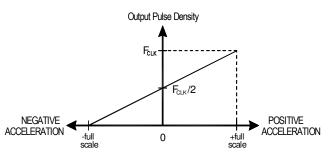

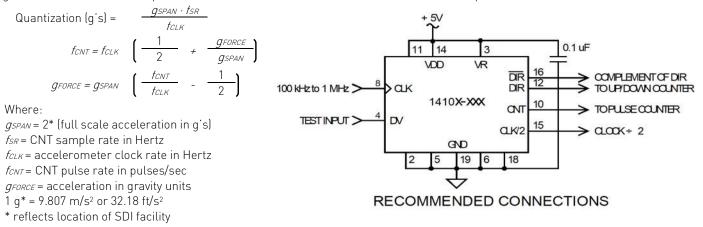

The Model 1410 produces a digital pulse train in which the density of pulses (number of pulses per second) is proportional to applied acceleration. It requires a single +5 volt power supply and a TTL/CMOS level clock of 100kHz-1MHz. The output is ratiometric to the clock frequency and independent of the power supply voltage. Two forms of digital signals are provided for direct interfacing to a microprocessor or counter. The sensitive axis is perpendicular to the bottom of the package, with positive acceleration defined as a force pushing on the bottom of the package. External digital line drivers can be used to drive long cables or when used in an electrically noisy environment.

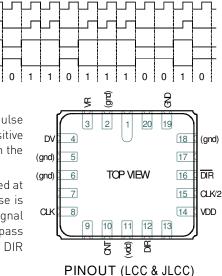

### SIGNAL DESCRIPTIONS

VDD and GND (power): Pin 14 (VDD) & pin 19 (GND). Additionally, tie pins 3

& 11 to VDD & pins 2, 5, 6 & 18 to GND.

<u>CLK (input)</u>: Pin 8. Reference clock input. This hysteresis threshold input must be driven by a 50% duty cycle square wave signal. Factory Calibration is performed at 250 kHz, which is the recommended clock frequency for best results. Operation at frequencies as low as 100 kHz or as high as 1 MHz are possible, however a slight bias shift may result.

<u>CNT (output):</u> Pin 10. Count output. A return-to-zero type digital pulse stream whose pulse width is equal to the input CLK logic high time. The CNT pulse rate increases with positive acceleration. The device experiences positive (+1g) acceleration with its lid facing up in the earth's gravitational field. This signal is meant to drive an up-counter directly.

<u>DIR and DIR (output)</u>: Pins 12 & 16 respectively. Direction output. This output is updated at the fall of each clock cycle. It is high during clock cycles when a high going CNT pulse is present and low during cycles when no CNT pulse is present. A non- return-to-zero signal meant to control the count direction (i.e. up or down) of a counter. DIR can be low pass filtered to produce an analog measure of the acceleration. DIR is the complement of DIR and is provided for use in driving differential transmission lines.

DV (input): Pin 4. Deflection Voltage. Normally left open. A test input that applies an

electrostatic force to the sense element, simulating a positive acceleration. The nominal voltage at this pin is  $\frac{1}{3}$ VDD. DV voltages higher than required to bring the output to positive full scale may cause device damage.

<u>VR (input)</u>: Pin 3. Voltage Reference. Tie directly to VDD (+5V). A 0.1µF bypass capacitor is recommended at this pin.

<u>CLK/2 (output)</u>: Pin 15. Clock divided by 2. A buffered clock output whose frequency equals CLK divided by 2. \*\* Pins 1, 7, 9, 13, 17, and 20 are reserved for future use and should remain unused \*\*

<u>USING THE COUNT (CNT) OUTPUT:</u> Pulses from the CNT output are meant to be accumulated in a hardware counter. Each pulse accumulation or sample, reflects the average acceleration (change in velocity) over that interval. The sample period or "gate time" over which these pulses are accumulated determines both the bandwidth and guantization of the measurement.

SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

# MODEL 1410 DIGITAL SURFACE MOUNT ACCELEROMETER

The first equation above shows that as the sample rate is reduced (i.e. a longer sample period), the quantization becomes finer but bandwidth is reduced. Conversely, as the sample rate is increased, quantization becomes coarser but the bandwidth of the measurement is increased. The second and third equations show how the CNT pulse frequency equates to the applied g-force. When using a frequency counter to monitor the CNT output pulse rate, a counter with a DC coupled input must be used. The CNT output is a return-to-zero signal whose duty cycle varies from zero to fifty percent, from minus full scale to positive full-scale acceleration. A frequency counter with an AC coupled input will provide an erroneous reading as the duty cycle varies appreciably from fifty percent. The figure to the left illustrates how the CNT and DIR outputs vary as the accelerometer is subjected to accelerations from minus full scale (-FS) to plus full scale (+FS).

$\text{-FS} \begin{cases} \text{DIR} \\ \text{CNT} \end{cases}$ • 0 Hz -<sup>1</sup>/<sub>2</sub>FS \_\_\_\_\_ n п +<del>]</del>FS-(cNT <u>nnn nnn nnn nnn nnn + ³</u>fo +<sup>3</sup>FS+ **f** dir +ES⊀  $\int_{CNT} nnnnnnnnnnnnnnnnnnn + F_{C}$

$\Delta f \approx k (V_{DV} - \frac{1}{3} V_{DD})^2$

#### DEFLECTION VOLTAGE (DV) TEST INPUT: This test input applies an electrostatic force

to the sense element, simulating a positive acceleration. It has a nominal input impedance of 32 k $\Omega$  and a nominal open circuit voltage of  $\frac{1}{3}V_{DD}$ . For best accuracy during normal operation, this input should be left unconnected or connected to a voltage source equal to  $\frac{1}{3}$  of the V<sub>DD</sub> supply.

The change in output pulse rate  $[\Delta \hbar]$  is proportional to the square of the difference between the voltage applied to the DV input  $(V_{DV})$  and  $\frac{1}{2}V_{DD}$ . Only positive shifts in the output pulse rate may be generated by applying voltage to the DV input. When voltage is applied to the DV input, it should be applied gradually. The application of DV voltages greater than required to bring the output to positive full scale may cause device damage. The proportionality constant (k) varies for each device and is not characterized.

<u>ESD and LATCH-UP CONSIDERATIONS</u>: The model 1410 accelerometer is a CMOS device subject to damage from large electrostatic discharges. Diode protection is provided on the inputs and outputs but care should be exercised during handling to assure that the device is placed only on a grounded conductive surface. Individuals and tools should be grounded before coming in contact with the device. Do not insert the model 1410 into (or remove it from) a powered socket.

#### RECOMMENDED CONNECTIONS

<u>RoHS Compliance:</u> The model 1410 does not contain elemental lead and is RoHS compliant.

<u>Soldering</u>: Solder reflow should not exceed 239°C, exceeding this temperature may result in permanent damage

<u>Pre-Tinning of Accelerometer Leads is Recommended:</u> To prevent gold migration embrittlement of the solder joints, it is best to pre-tin the accelerometer leads.

<u>Solder Contact Plating Information:</u> The plating composition and thickness for the solder pads and castellations on the "L"

suffix (LCC) package are 60 to 225 micro-inches thick of gold (Au) over 80 to 350 micro-inches thick of nickel (Ni) over a minimum of 5 micro-inches thick of moly-manganese or tungsten refractory material. The J-Lead package top layer is 100 to 225 microinches thick of 99.7% gold (Au) over 80 to 350 microinches thick of electroplated nickel (Ni).

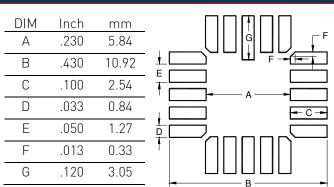

<u>Recommended Solder Pad Pattern</u>: The recommended solder pad size and shape for both the LCC and J LCC packages is shown in the diagram and table below. These dimensions are recommendations only and may or may not be optimum for your particular soldering process.

## Do not use ultrasonic cleaners. Ultrasonic cleaning will void the warranty and may break internal wire bonds.

SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

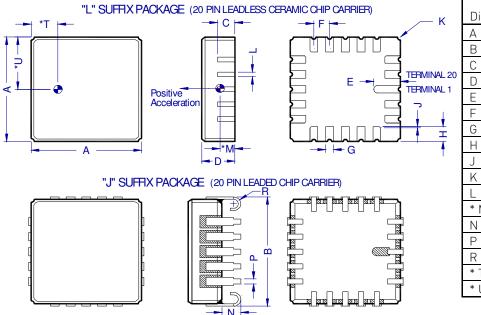

## PACKAGE DIMENSIONS

- 1. \*Dimensions "M," "T," and "U" locate sensing element's center of mass.

- 2. Lid is electrically tied to terminal 19 (GND).

- Controlling dimension: Inch. З.

- Terminals are plated with 60 microinches min gold over 80 microinches min nickel. This plating specification does not apply 4. to the Pin-1 identifier mark on the bottom of the J-lead package version.

- 5. Package: 90% min alumina (black), lid: solder sealed kovar.

|     | Inches      |       | Millimeters |      |  |

|-----|-------------|-------|-------------|------|--|

| Dim | Min         | Max   | Min         | Max  |  |

| А   | 0.342       | 0.358 | 8.69        | 9.09 |  |

| В   | 0.346       | 0.378 | 8.79        | 9.60 |  |

| С   | 0.055       | 5 TYP | 1.40 TYP    |      |  |

| D   | 0.095       | 0.115 | 2.41        | 2.92 |  |

| E   | 0.085       | 5 TYP | 2.16 TYP    |      |  |

| F   | 0.050       | BSC   | 1.27        | 3SC  |  |

| G   | 0.025 TYP   |       | 0.64 TYP    |      |  |

| Н   | 0.050 TYP   |       | 1.27 TYP    |      |  |

| J   | 0.004 x 45° |       | 0.10 x 45°  |      |  |

| Κ   | 0.010 R TYP |       | 0.25 R TYP  |      |  |

| L   | 0.016 TYP   |       | 0.41 TYP    |      |  |

| * M | 0.066       | TYP   | 1.68 TYP    |      |  |

| Ν   | 0.050       | 0.070 | 1.27        | 1.78 |  |

| Ρ   | 0.017 TYP   |       | 0.43 TYP    |      |  |

| R   | 0.023 R TYP |       | 0.58 R TYP  |      |  |

| * T | 0.085 TYP   |       | 2.16 TYP    |      |  |

| * U | 0.175 TYP   |       | 4.45 TYP    |      |  |

SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE